高速インターフェースの基準クロックに最適な超低ジッタLVDSクロック水晶発振器

★ 低ジッタ 50fs (@156.250MHz) 及び 55fs (@125MHz) の差動LVDS出力クロック

高速化するシリアル通信インターフェース仕様に対応する超低位相ジッタのLVDSクロックです。

シリーズではLV-PECL 出力の CP220もあります。

従来品のシリーズに比べて大幅に位相ノイズ特性が低減されており、かつ高速スイッチング (Tr/Tf=0.2ns Typ.)

によりFPGAのリファレンスクロックとして最適な特性です。

即納の在庫ラインアップ も充実させています。

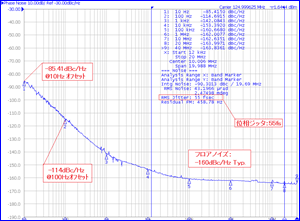

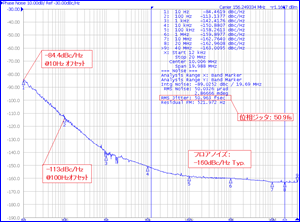

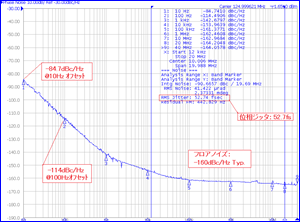

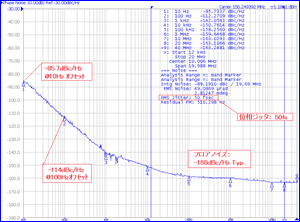

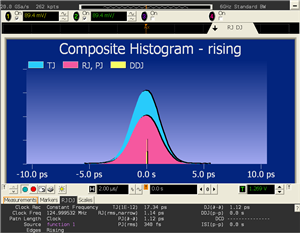

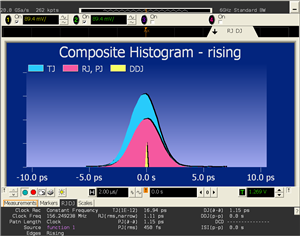

・位相ジッタ特性(各サンプルでの実測値)*画像をクリックすると拡大表示します

| CL224BB-125.000MHz ( +3.3Vdd/LVDS ) | CL224BB-156.250MHz ( +3.3Vdd/LVDS ) |

|

|

|

| CL22VBB-125.000MHz ( +2.5Vdd/LVDS ) | CL22VBB-156.250MHz ( +2.5Vdd/LVDS ) |

|

|

|

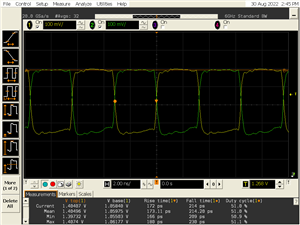

・波形特性 (各サンプルでの実測値)*画像をクリックすると拡大表示します

| CL224BC-125.000MHz ( +3.3Vdd/LVDS ) | CL224BC-156.250MHz ( +3.3Vdd/LVDS ) |

|

|

|

・トータルジッタ特性 *画像をクリックすると拡大表示します

| CL224BB-125.000MHz ( +3.3Vdd/LVDS ) | CL224BB-156.250MHz ( +3.3Vdd/LVDS ) |

・Xilinx / Vertex-6 FPGA GTP トランシーバー用リファレンスクロックの位相ノイズ要求仕様との比較

・Xilinx / 7シリーズ FPGA GTX/GTH/GTP トランシーバー用リファレンスクロックの位相ノイズ要求仕様との比較